I have been working with my FPGA boards to attempt to display a test pattern on a VGA monitor. For my experiments, I bought a small VGA monitor*. It has a VGA input, as well as a HDMI input, so I can use it with all of my FPGAs, since the Zybo only has HDMI ports.

Hardware

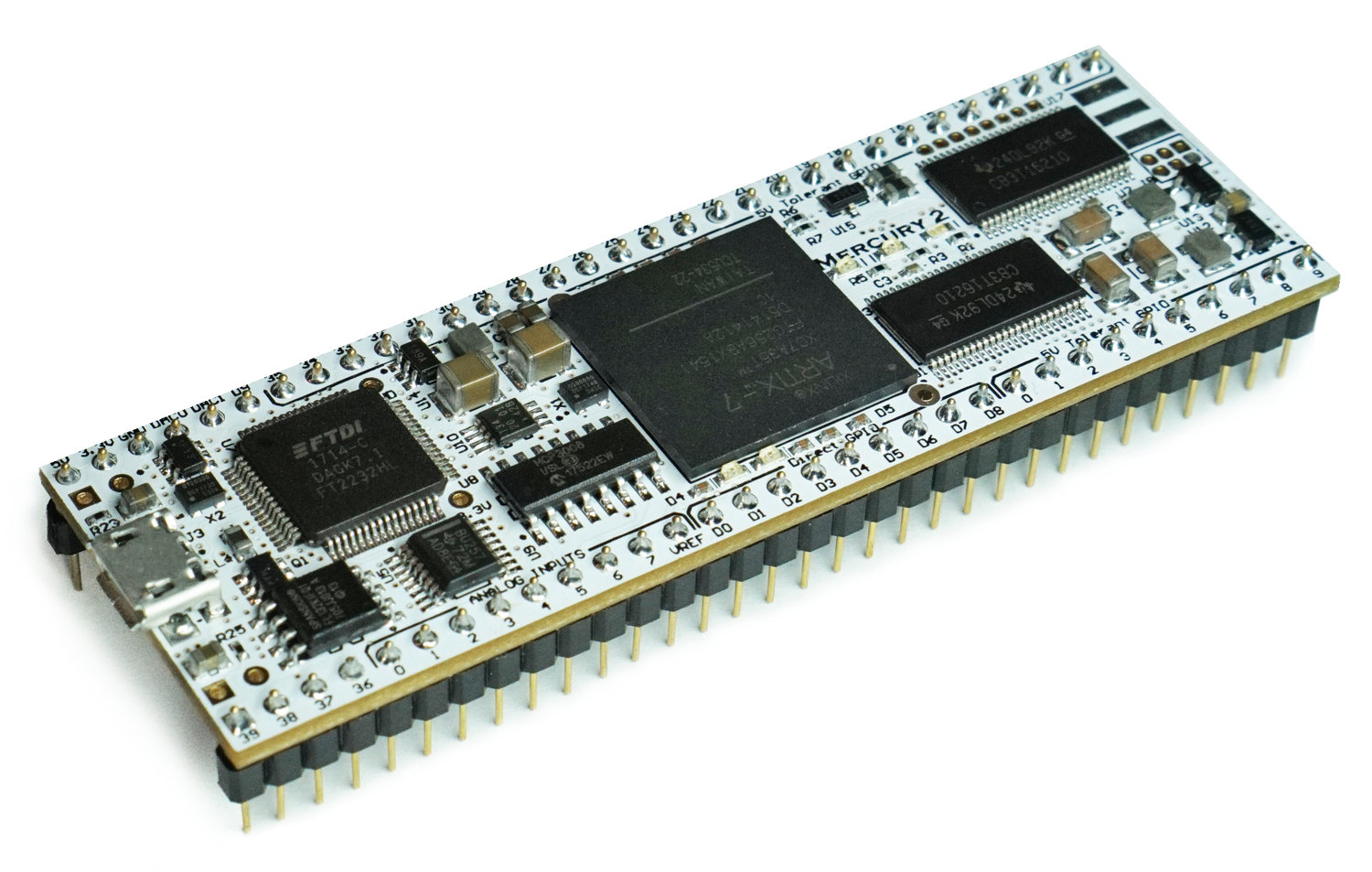

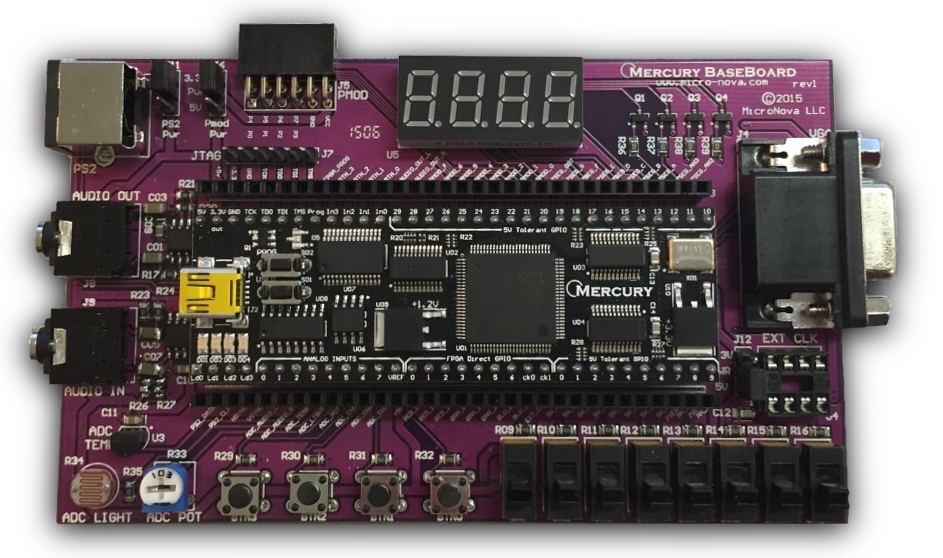

I am using my Mercury 2 with the Mercury baseboard attachment, as it has a VGA port on it. I will also attempt to get it working on my Nexys A7*.

VGA Code

I found some great VGA Verilog code on TinyVGA.com that I was able to utilize as the base foundation for my VGA experiments.

Here is the altered Verilog code for my VGA device.

// Author: unknown

// www.TinyVGA.com

module vga2(clk, red,green,blue,hsync,vsync);

// Input clk, 50 MHz Oscillator

input clk;

// VGA outputs

output red;

output green;

output blue;

output hsync;

output vsync;

reg [9:0] hcount; // VGA horizontal counter

reg [9:0] vcount; // VGA vertical counter

reg [2:0] data; // RGB data

wire hcount_ov;

wire vcount_ov;

wire videosignal_active;

wire square_active;

wire hsync;

wire vsync;

reg vga_clk;

// VGA mode parameters

parameter hsync_end = 10'd95,

hdat_begin = 10'd143,

hdat_end = 10'd783,

hpixel_end = 10'd799,

vsync_end = 10'd1,

vdat_begin = 10'd34,

vdat_end = 10'd514,

vline_end = 10'd524;

always @(posedge clk)

begin

vga_clk = ~vga_clk;

end

always @(posedge vga_clk)

begin

if (hcount_ov)

hcount <= 10'd0;

else

hcount <= hcount + 10'd1;

end

assign hcount_ov = (hcount == hpixel_end);

always @(posedge vga_clk)

begin

if (hcount_ov)

begin

if (vcount_ov)

vcount <= 10'd0;

else

vcount <= vcount + 10'd1;

end

end

assign vcount_ov = (vcount == vline_end);

assign videosignal_active = ((hcount >= hdat_begin) && (hcount < hdat_end))

&& ((vcount >= vdat_begin) && (vcount < vdat_end));

assign square_active = ((hcount >= 250) && (hcount < 500))

&& ((vcount >= 250) && (vcount < 500));

assign hsync = (hcount > hsync_end);

assign vsync = (vcount > vsync_end);

assign red = (videosignal_active) & (square_active) ? data[0] : 0;

assign green = (videosignal_active) ? data[1] : 0;

assign blue = (videosignal_active) ? data[2] : 0;

// generate "image"

always @(posedge vga_clk)

begin

// data <= (vcount[2:0] ^ hcount[2:0]);

data <= (vcount[1:0] ^ hcount[2:1]);

end

endmoduleI altered the original code to include a box that only displays for the red pixels, making a yellow box in my test pattern.

Here is the result

A few years ago, I was able to successfully setup a Pong game (from https://www.fpga4fun.com/) that used a potentiometer to move the paddle, but I can’t find my original Verilog from that project. I’d like to do it again. It would be nice if I could have a display for the SAP-1 implementation that I’m working on.