SAP-1 on FPGA Ep. 2 - Simple Seven Segment

In my previous post about the SAP-1, I discussed using the LEDs on my Nexys 7 to display the results of any data that I want to produce. I mentioned that the 8 digit 7-segment display was above my head.

This post is an attempt to make sense of it and get it working as best I can. I’m going to start by simply wiring up the output ports for the Seven Segment display to the top level circuit.

Here is a simple implementation:

Verilog

module sevseg_top(

input CLK100MHZ,

output [6:0] segs,

output [7:0] AN

);

assign segs = 7'b1001111;

assign AN[7:0] = 8'b11111110;

endmodule

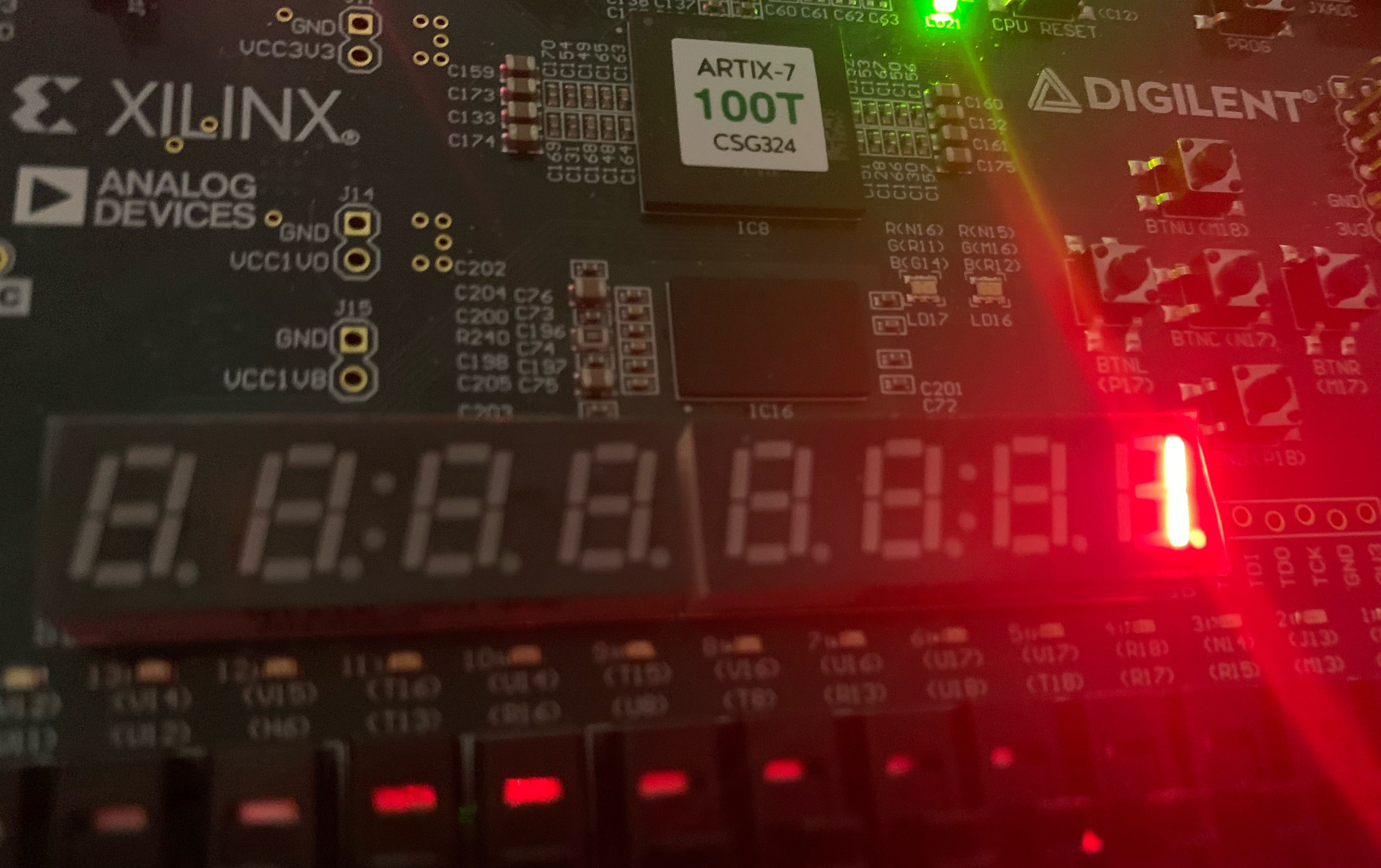

And, the result:

The next steps will be to move this model off to its own module and create a way to select the 8 digits in order from 7 down to 0. Let’s start by getting the module defined.

Verilog

module sevseg_top(

input CLK100MHZ,

input CPU_RESETN,

output [6:0] segs,

output [7:0] AN

);

assign segs = 7'b1001111;

wire stop;

counter_8bit counter(

CLOCK100MHZ,

~CPU_RESETN,

stop,

AN);

endmodule

As you can see, I added a Reset input and a stop wire. Here is the implementation for the counter_8bit.

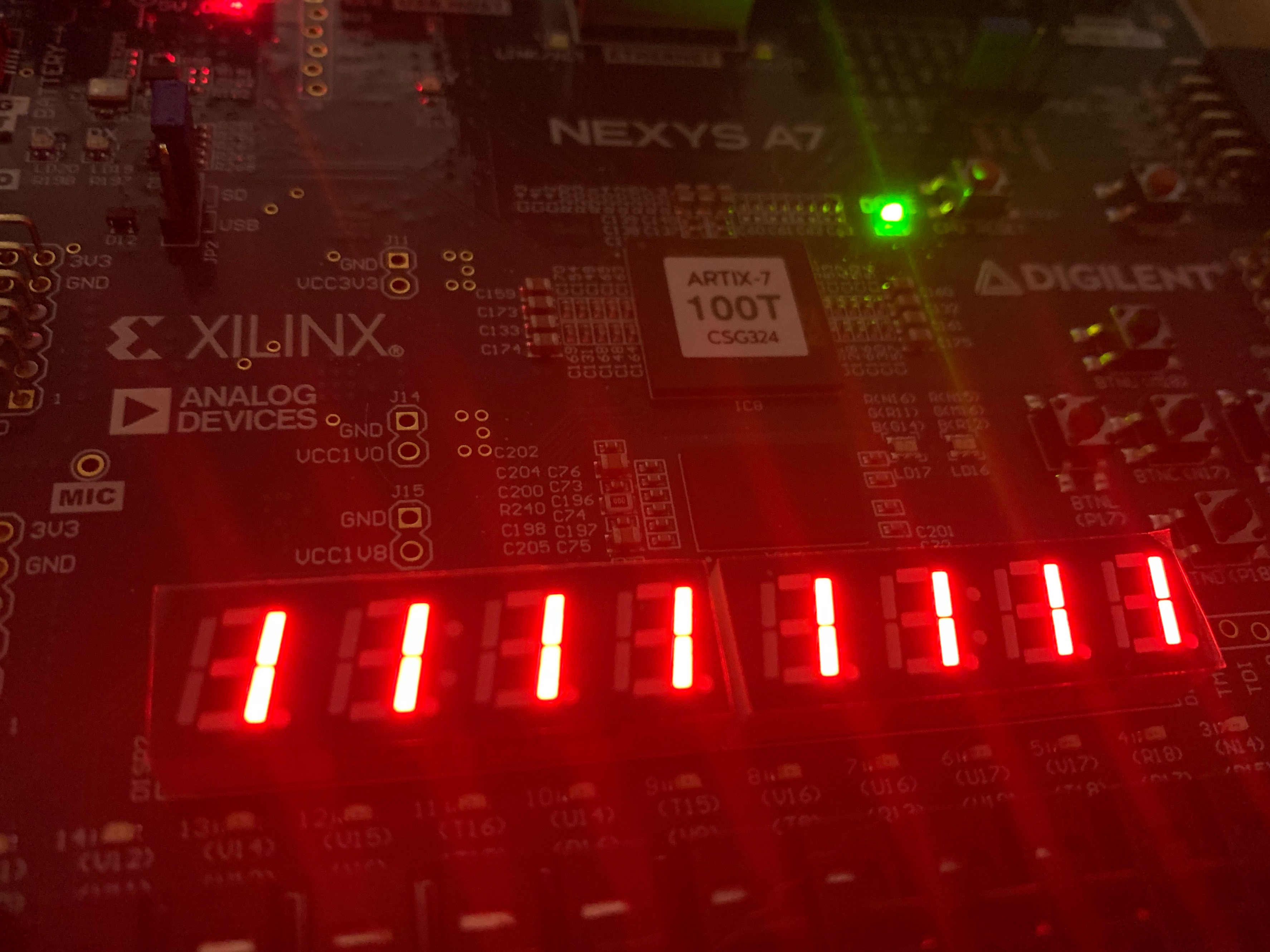

Here are the results:

This is where I get tripped up. Now, I need to find a way to define the digits, then assign them to a particular digit (AN signal)

Let’s start by defining all of the segments into hex digits.

Verilog

module hex_to_seven_segment(

input [3:0] hex,

output reg [6:0] segment

);

always @(*) begin

case (hex)

4'h0: segment = 7'b1000000; // 0

4'h1: segment = 7'b1111001; // 1

4'h2: segment = 7'b0100100; // 2

4'h3: segment = 7'b0110000; // 3

4'h4: segment = 7'b0011001; // 4

4'h5: segment = 7'b0010010; // 5

4'h6: segment = 7'b0000010; // 6

4'h7: segment = 7'b1111000; // 7

4'h8: segment = 7'b0000000; // 8

4'h9: segment = 7'b0011000; // 9

4'ha: segment = 7'b0001000; // A

4'hb: segment = 7'b0000011; // B

4'hc: segment = 7'b0100111; // C

4'hd: segment = 7'b0100001; // D

4'he: segment = 7'b0000110; // E

4'hf: segment = 7'b0001110; // F

default: segment = 7'b1111111; // Blank

endcase

end

endmodule

Now that I have that defined, I’m not really sure what I should do with it. I know I need to find a way to set a single value on a digit so that each time the digit is accessed, it displays the same thing. Then, I need to find a way to cycle through the segments. I know that I do this by setting the appropriate AN to low while setting the segments to high (using the decoder).

At this point, I ran into so many difficulties that I had to take a break from it for awhile. I will revisit the topic soon, after I’ve had a chance to learn about Verilog and digital design more.